Forschungsprojekt

Analog Sensor Frontend with RISC-V

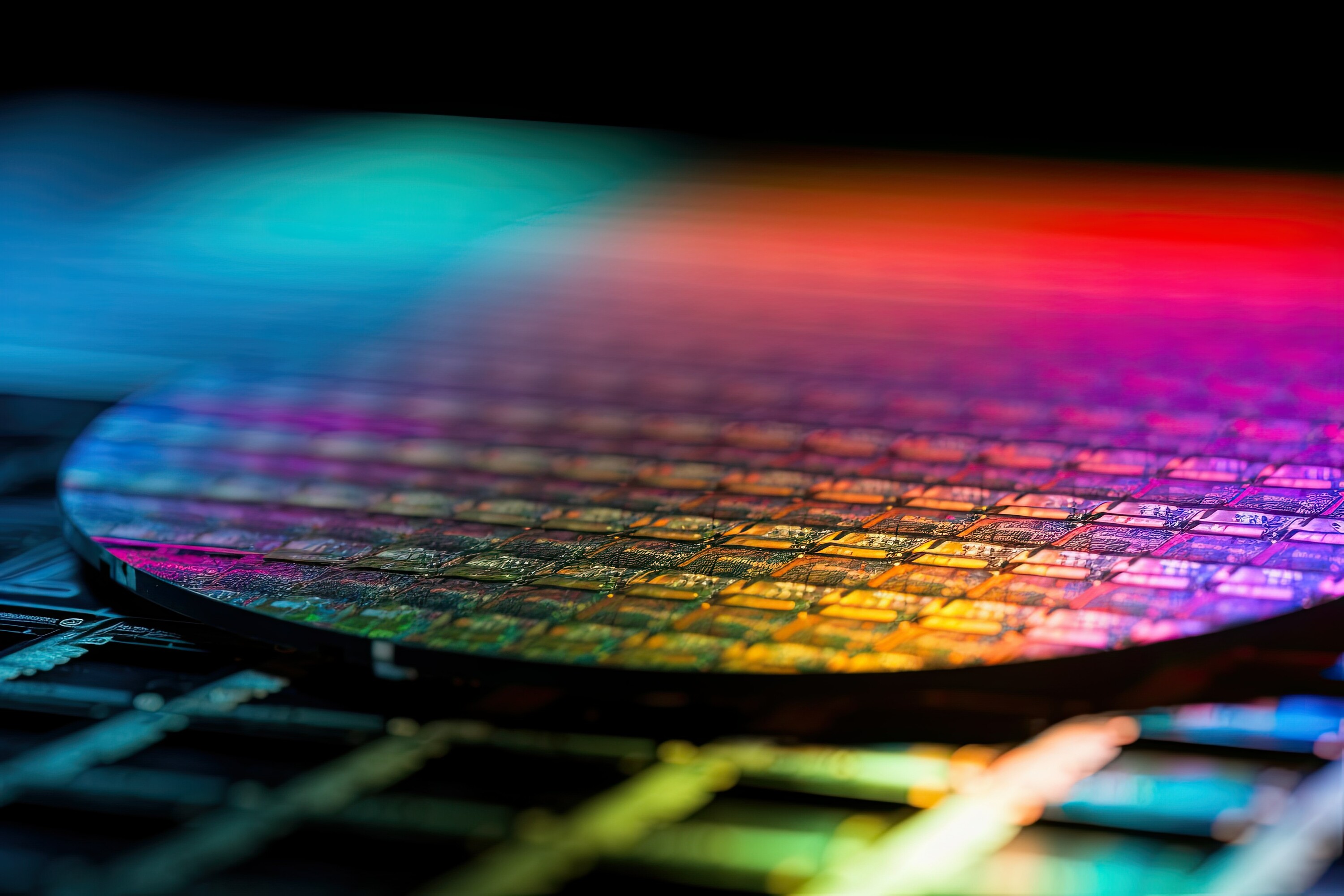

Im Rahmen dieses Masterprojekts wurde ein RISC-V-basierter, applikationsspezifischer Mikrochip (ASIC) entwickelt, der als Sensor-Frontend dient.

Der Zweck besteht darin, einen Demonstrationschip in einem 180nm-Fertigungsprozess zu entwickeln, der einen RISC-V-Mikroprozessorkern in Kombination mit einem analogen Frontend in die IP-Bibliothek des Instituts für Mikroelekronik, Embedded Systems und Sensorik (IMES) integriert.