Entwicklung eines Konzepts für einen isolierten Vektor-Netzwerkanalysator

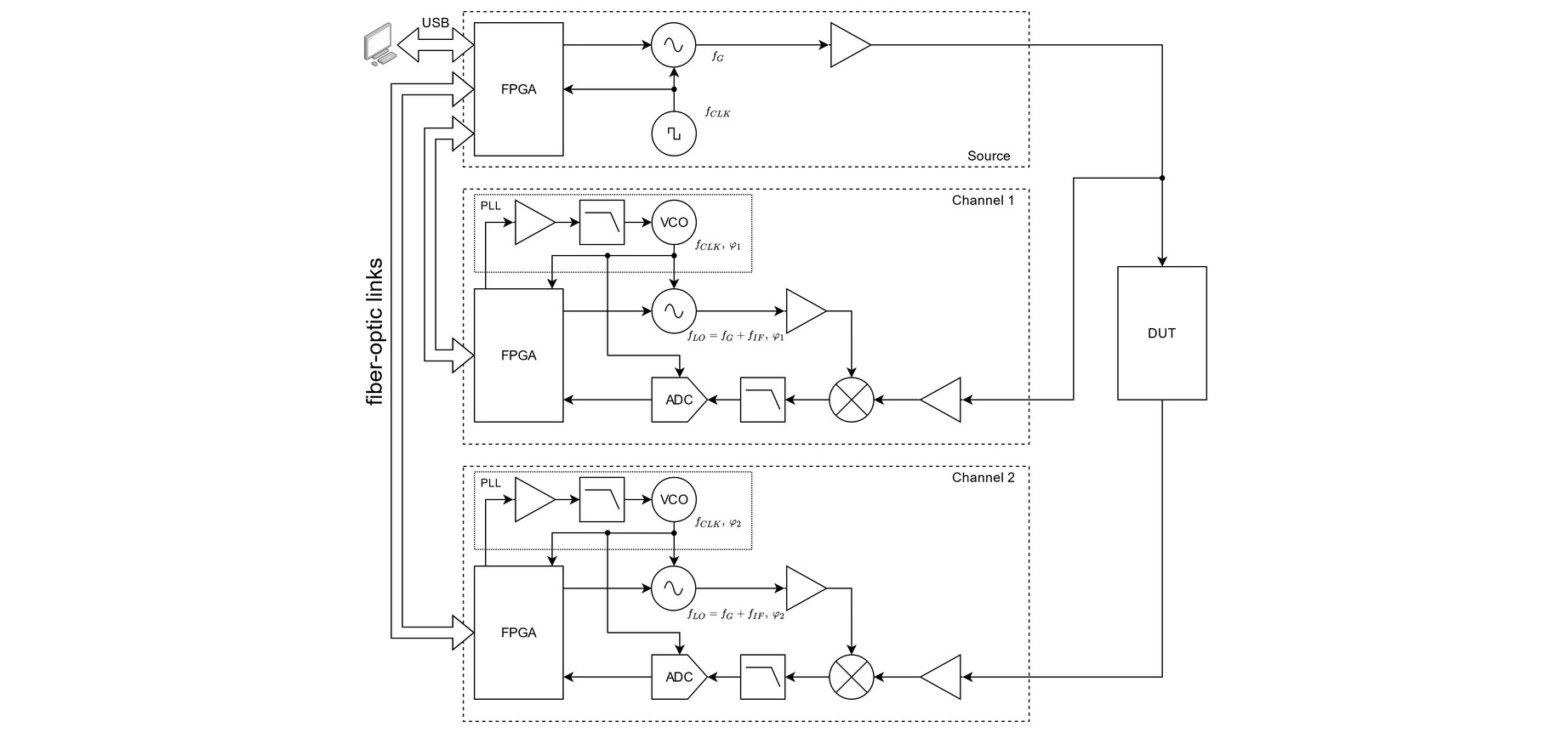

Einleitung: Vektorielle Netzwerkanalysatoren werden in erster Linie zur Messung von Netzwerkparametern, beispielsweise S-Parameter, von elektrischen Schaltungen verwendet. Diese Parameter werden zur Charakterisierung von elektrischen Netzwerken wie beispielsweise Filtern, Verstärkern und mehr verwendet. Ein Nachteil der meisten handelsüblichen Vektor-Netzwerkanalysatoren ist, dass alle Ein- und Ausgänge auf ein gemeinsames Massepotential bezogen sind, was den Einsatz bei Messungen erschwert, bei denen eine galvanische Isolation erforderlich ist. Um dieses Problem zu überwinden, wurde in dieser Arbeit ein Konzept für einen galvanisch isolierten Vektor-Netzwerkanalysator entwickelt. Das System soll aus drei separaten Einheiten bestehen, die vollständig galvanisch voneinander isoliert sind. Zwei Einheiten sind dedizierte Messkanäle, die dritte Einheit dient als Basis mit Signalquelle. Die Kommunikation zwischen den Einheiten erfolgt über optische Fasern. Der Schwerpunkt lag auf dem erreichbaren Phasenfehler des Messsystems, der vollständig von der Synchronität der Messkanäle zueinander abhängig ist. Die Anforderungen sind mit einem Phasenfehler von 0.5° bei 50 MHz vorgegeben, was einer Zeitverzögerung von 27.8 ps entspricht.

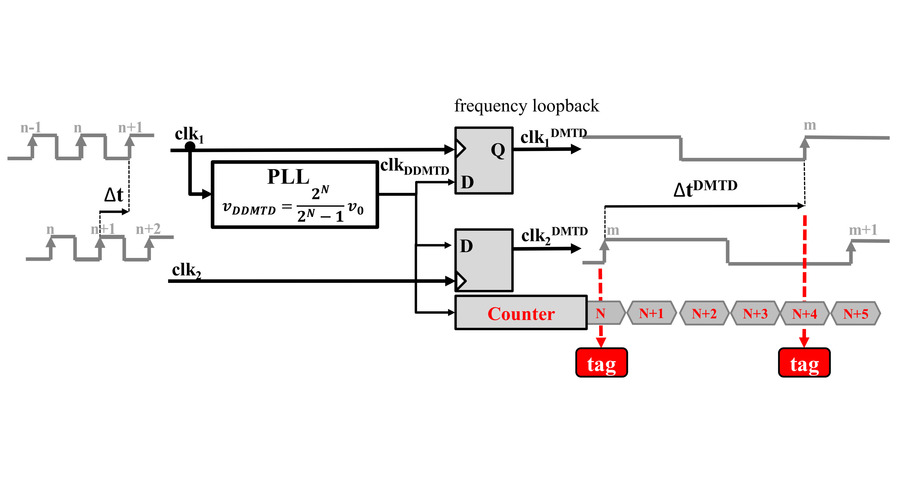

Vorgehen: Unter Verwendung bekannter Techniken wie Phasenregelschleifen und einiger cleverer Ideen zur Implementierung eines hochauflösenden Phasendetektors aus dem White Rabbit-Netzwerk, einem CERN-Projekt, wurde ein Systemkonzept entwickelt. Zuerst wurden die einzelnen Komponenten des Systems, einschließlich Phasendetektor und Messkanal, in MATLAB Simulink modelliert. Das Modell wurde dann schrittweise erweitert, um das gesamte System einschließlich der Signallaufzeiten im Kommunikationspfad zu erfassen.

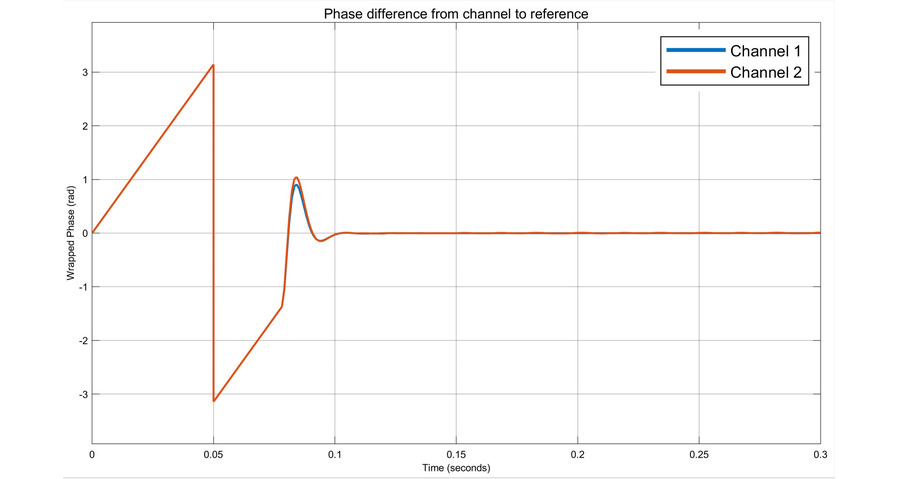

Ergebnis: Die Simulationsergebnisse zeigen, dass das System funktioniert und die Kanäle mit ausreichend hoher Genauigkeit synchronisiert werden, dennoch gibt es Potential für Verbesserungen.

Die Ergebnisse dieser Arbeit können als Grundlage für einen Hardware-Prototyp verwendet werden, um das Konzept in einer realen Implementierung zu validieren.