## Design of a fully integrated Buck-Boost Converter ASIC

## A small Buck-Boost Converter ASIC with integrated switches on a commercial 0.35 um process node

Students

Patrick Jansky

Matthias Meyer

Introduction: This part of the project focuses on the post-layout phase of a project, which was divided into pre-layout and post-layout stages. The project was initiated by Sonova AG, with the objective of designing a compact 200 mA DC/DC converter for the potential integration into the charging case of their hearing devices. The device should generate a stable 5 V supply from a USB power source with a input range of 4.35 V to 5.5 V, in accordance with the USB specification. In addition to the analog circuits in the switching converter, a digital SPI interface was added which allows for digital configuration of the device settings.

Approach: During this second phase of this project, we successfully finished the chip design and were able to meet the tape-out deadline. Afterwards, in preparation to receiving the samples, we created the test setup, creating both custom hardware and software for semi-automated chip testing from scratch. This allowed us to quickly start testing and gathering data as soon as the samples arrived.

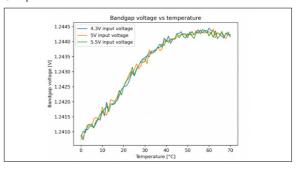

Result: The SPI interface was successfully validated with a Python driver, enabling register read/write operations to configure the chip on the fly. While the power-on reset and bandgap voltage reference were inside the specifications, the internal current reference showed a deviation of about 38.8% from the simulation. A likely cause is a not anticipated tolerance deviation in the 'rnp1' resistors used. The oscillator showed a deviation of about 54.7% from the simulation. Fortunately, both of these problems had a minimal impact and the function of the IC.

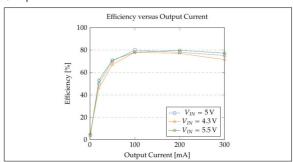

Both the response to a load step as well as the conversion efficiency of the chip are satisfactory and within the range specified. The efficiency was measured under various load conditions and with varied input voltages and can be seen in the second plot below. The converter achieves a peak efficiency of 80% at a 100mA load.

Overall, the samples characterized largely conform with the simulated values. The chips were even able to sustain loads currents of up to 300mA, an increase of 50% over the designed maximum, while maintaining correct operation.

## Bandgap voltage vs temperature measured Own presentment

Conversion efficiency at frequency = 1.17 MHz; Data points for 20 mA and 50 mA are estimates based on interpolation

Own presentment

## Compilation of the main measured device characteristics compared with their simulated values Own presentment

| Parameter              | Information & Test Conditions                                                      | Sim   | Min   | Max    | Unit |

|------------------------|------------------------------------------------------------------------------------|-------|-------|--------|------|

| <b>Buck-Boost Conv</b> | erter                                                                              |       |       |        |      |

| Vour                   | Average output voltage                                                             | 5.01  | 4.99  | 5.03   | V    |

| $V_{OUT,PP}$           | Ripple voltage on $V_{OUT}$ , $I_{LOAD} = 200 \text{ mA}$                          | 13.2  |       | 200    | mV   |

| Line Regulation        | $V_{IN} = 4.3 - 5.5 \text{ V}, I_{LOAD} = 200 \text{ mA}$                          | < 1   |       | < 1    | %    |

| Load Regulation        | $V_{IN} = 5.0 \text{ V}, I_{LOAD} = 0 - 200 \text{ mA}$                            | < 1   |       | < 1    | %    |

| fsw                    | Converter PWM frequency                                                            | 1000  | 1170  | 2630   | kHz  |

| η                      | Efficiency @ $f_{SW} = 1$ MHz, $I_{LOAD} = 200$ mA                                 | 83.48 |       | 80.0   | %    |

| ω                      | Regulation loop crossover frequency                                                | 20    |       | 30     | kHz  |

| PM                     | Regulation loop phase margin                                                       | 45    |       | 55     | 0    |

| Current Consump        | ption                                                                              |       |       |        |      |

| I <sub>O,VDDL</sub>    | Quiescent current in $V_{DDL}$ , $V_{DDL} = 5 \text{ V}$ , $V_{RST} = 0 \text{ V}$ | -     |       | 1.12   | mA   |

| I <sub>IN,STBY</sub>   | Input current $V_{DDL} = V_{IN} = 5 \text{ V}$ , $I_{LOAD} = 0 \text{ mA}$         | 1.03  |       | 19     | mA   |

| I <sub>SH,VDDL</sub>   | Shutdown current in $V_{DDL}$ , $V_{DDL} = 5 \text{ V}$ , $V_{RST} = 5 \text{ V}$  | -     |       | < 10.0 | μА   |

| ILEAK,VIN              | Leakage current in $V_{IN}$ , $V_{IN} = 5 \text{ V}$ , $V_{RST} = 5 \text{ V}$     | -     |       | 140    | μΑ   |

| Miscellaneous          |                                                                                    |       |       |        |      |

| Vuvlo                  | Positive-going UVLO threshold voltage                                              | 3.4   |       | 3.72   | V    |

| $V_{FB} = V_{BGP}$     | Internal FB reference voltage                                                      | 1250  | 1239  | 1290   | mV   |

| IREF                   | Internal reference current                                                         | 10.5  | 14.11 | 14.88  | μΑ   |

| R <sub>DS,m,HS</sub>   | High-Side switch ON-Resistance                                                     | 58.3  |       |        | mΩ   |

| R <sub>DS,on,LS</sub>  | Low-Side switch ON-Resistance                                                      | 37    |       |        | mΩ   |

Advisor Lars Kamm

Subject Area Electrical Engineering